System-Level Tutorial Lesson 4: Exploring Phase-Locked Loops

Contents

What You Will Learn

In this tutorial you will learn how to test and use one of RF.Spice's more complex black-box virtual blocks with a large number of parameters: the analog phase-locked loop (PLL).

Overview of PLL Operation

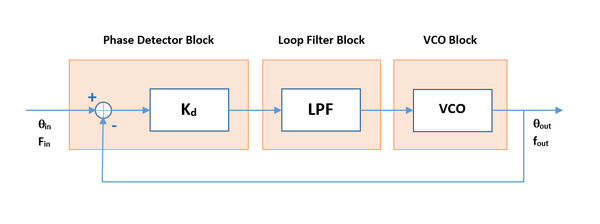

A phase-locked loop (PLL) is a feedback control system that generates an output signal whose frequency and phase are related to the frequency and phase of an input signal also known as the reference signal. At the heart of a PLL there is a voltage-controlled oscillator (VCO) along with a phase detector. The oscillator initially generates a periodic signal with a certain free-running frequency. The phase detector compares the phase of the VCO signal with the phase of the input periodic signal and adjusts the oscillator to keep the phases matched through the feedback loop. It is clear that keeping the input and output phase in lock step also implies keeping the input and output frequencies the same.

To better understand the operation of the PLL block, consider the highly simplified schematic shown in the figure below. The output of the internal lowpass filter section is directly fed into the input of the internal VCO section, and the output of the VCO section is directly fed back into one of the two inputs of the internal phase detector section. The lowpass filter is a simple RC filter, and you can adjust the values of RLPF and CLPF. The internal VCO section involves a timing RC circuit (integrator), and you can adjust the values of Rtime and Ctime. The nonlinear voltage-controlled source Bpd generates a scaled version of the difference signal (Vin-Vout) with a scaling factor of Kd. The transconductance of the voltage-controlled current source Gvco is equivalent to the conversion gain Kf of the VCO.

Testing the APLL Device

The following is a list of parts needed for this part of the tutorial lesson:

| Part Name | Part Type | Part Value |

|---|---|---|

| V1 | Voltage Source | Waveform TBD |

| X1 | Analog Phase-Locked Loop (APLL) | Defaults |

| R1 | Resistor | 50 |

| IC1 | Transient Initial Condition Marker | 1V |

Place and connect the parts as shown in the Figure below.

You can access the APLL device from Menu > Parts > Spectral Processing Blocks > Phase Locked Loop (PLL) Block. The default free-running frequency of the PLL's VCO is set to 1kHz. Keep all the default values.

The Transient Initial Condition Marker labeled IC1 with a prescribed voltage of 1V is placed at the output of the square wave VCO output to the give the oscillator circuit the initial kick.

Define a sinusoidal waveform for your voltage source according to the table below:

| Offset Voltage | 0 |

|---|---|

| Peak Amplitude | 1 |

| Frequency | 1kHz |

| Delay Time | 0 |

| Damping Factor | 0 |

Run a Transient Test of this circuit with the parameters specified below:

| Start Time | 0 |

|---|---|

| Stop Time | 10m |

| Linearize Step | 1u |

| Step Ceiling | 1u |

| Preset Graph Plots | v(1), v(4), v(5) |

The voltage graphs are shown in the figure below. The RF.Spice's APLL device provides a square wave output as well as a triangular wave output, both of which are phase-locked with the input signal. This can be clearly seen from the figure by comparing the phases of the red input sinusoid and the light blue output triangular wave.

Examining the Effect of the Transient Initial Conditions

If the transient initial condition at the output of the VCO is zero, the initial phase difference will be zero. As result, the output of the phase detector will be zero and the feedback loop will not work. That's why you set up the marker IC1 to impose a nonzero initial voltage at Node 5. At this part of the tutorial lesson, use the same circuit as above and run an transient test with the following parameters:

| Start Time | 0 |

|---|---|

| Stop Time | 100m |

| Linearize Step | 1u |

| Step Ceiling | 1u |

| Preset Graph Plots | v(2) |

The figure below shows the voltage at the output of the loop filter. It can be seen that this phase error signal fluctuates between 194mV and -196mV with a zero average. The output signal is thus locked in phase and frequency with the input signal.

Next, change the value of the initial voltage of the IC1 marker to -0.1V and run a new transient test with the same parameters as before. As the figure below shows, the PPL still locks but it takes a little longer than the previous case.

Investigating the Effect of a Frequency Step

Using the same circuit of the previous part and setting the value of IC1 voltage back to +1V, now change the frequency of the source signal to 1.05kHz. Note that the free-running frequency of the PLL is still the default 1kHz.

The figure below shows the voltage at the output of the loop filter. It can be seen that this phase error signal fluctuates between 194mV and -196mV with a zero average. The output signal is thus locked in phase and frequency with the input signal.