An Overview of Analog and Mixed-Mode Circuit Simulation

Contents

An Overview of Analog Circuit Simulation

An analog circuit consists of a source, one or more passive or active devices and a ground. The sources, devices and the ground are connected to one another using wires. Wires carry electric currents. The interconnections of wires create circuit nodes. Each node has a voltage, and each wire entering a node carries a current. A wire connecting two nodes forces the voltages of those two node to be equal. Analog circuits are governed by Kirchhoff’s current and voltage laws (KCL and KVL). Individual analog devices are characterized by v-i equations, which relate the terminal current(s) of a device to the voltages across those terminals or pins. Passive devices like resistors, capacitors and inductors are governed by linear v-i equations (Ohm’s law), while active devices like diodes and transistors are usually characterized by nonlinear v-i equations.

Sources supply your circuit with known voltages or currents. The voltages and currents at all other nodes of your circuit are the unknowns in an analog circuit simulation. Over the past 30 years, the faculty and graduate students at the University of California, Berkeley, have developed extensive computer algorithms for analog circuit simulation. This project, and the resulting computer code, are known as SPICE. B2.Spice A/D uses the Berkeley SPICE (with some modifications and enhancements) for all circuit simulations. Since SPICE's algorithms have been in wide-spread use by industry for a long period of time, you can be confident in the accuracy of the results you get from B2.Spice A/D. We have also incorporated major pieces of the XSPICE program from Georgia Institute of Technology. XSPICE expands the Berkeley SPICE by providing for mixed-mode simulation, a code modeling module that makes it easier to add new models, and inter-process communications. Further, we have modified the DC transfer function to allow for more general parameter sweeps, and we have added Monte Carlo simulations and parameterized AC and transient simulations.

SPICE algorithms incorporate the behavior a variety of devices including resistors, capacitors, inductors, mutual inductors, independent voltage and current sources, four types of dependent sources, switches, uniform distributed RC lines, and the five most common semiconductor devices: diodes, BJTs, JFETs, MOSFETS, and MESFETS. B2.Spice A/D uses the SPICE algorithms and offers the same circuit capabilities. The BSIM3v3.2 model is another piece that we have added to the simulation engine. This was developed by the bsim3 development team at UC Berkeley. SPICE offers default models of the semiconductor devices; however, the desired parameter values need to be specified. Default model parameters are available when you create a new model in the Device Editor. You can also specify additional device models if the defaults are not adequate.

SPICE provides several different types of analysis, including Operating Point (DS Bias), DC Sweep, AC sweep, and Transient. DC and Transient analyses are iterative processes which terminate when both of the following conditions are satisfied:

- Nonlinear branch currents converge to within a tolerance of 0.1% or 1 picoamp, whichever is larger.

- Node voltages converge to within a tolerance of 0.1% or 1 microvolt, whichever is larger.

Failure to converge in DC analysis usually results from incorrectly specifying circuit connections, initial values, or model parameters. Regenerative switching circuits or circuits with positive feedback will often fail to converge, unless the OFF option is used for some of the devices in the feedback path.

Two Distinct Simulation Modes

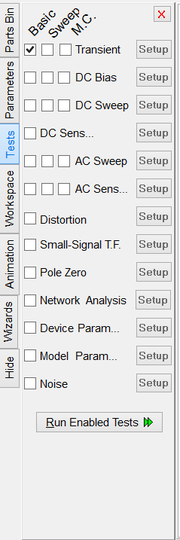

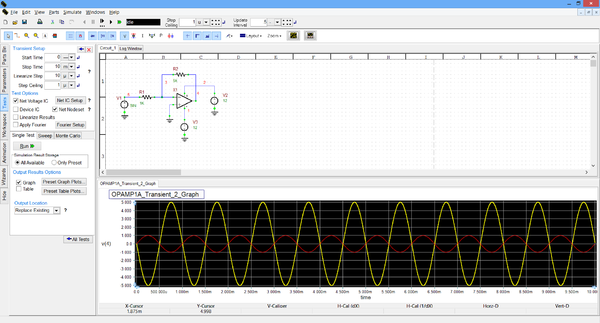

B2.Spice A/D now has two distinct simulation modes: interactive live "Simulations" and preset non-interactive "Tests". There are important differences between a Test and a Live Simulation. These differences must be understood before you can effectively use B2.Spice A/D.

A live "Simulation" is simply a continuous transient simulation, starting at time t = 0 and incrementing indefinitely by a user-defined time period. Simulations can be paused and continued but they run continuously until stopped, paused or reset. Simulations can be stimulated by Virtual Instruments such as Function Generator or Power Supply, can be measured by Virtual Instruments such as Oscilloscope, Ammeter, Voltmeter, etc. and can be manipulated in real time from the Circuit Parameters Panel in the Toolbox. Instead of using virtual instruments, you can also use regular voltage or current source devices to excite your circuits or use probes or circuit animation to display node voltages and currents.

"Tests", on the other hand, are run with preset and predefined sets of parameters. Tests are used to analyze your circuit in various time and frequency domains. These include a circuit's DC bias (operating point), transient and steady-state AC responses, its noise output, network characteristics, as well as various other responses. The results of tests are displayed on a graph or in a table, not on virtual instruments.

Running RF.Spice A/D Live Simulations

You can start a live time domain simulation of your circuit simply by pressing the green RUN ![]() button in the Main Toolbar. But getting meaningful results requires a few more steps. A simulation needs an input such as a source as well as a probe or some kind of virtual instrument to measure the result. Inputs can be source devices found in the supplied parts database. These include voltage sources or current sources that supply power to your circuit. Alternatively, you can use the Power Supply or Function Generator in the Virtual Instruments panel to set up stimuli. To measure the results, you can use the Virtual Oscilloscope, Voltmeter, Ammeter or one of the other meters found in the Virtual Instruments or you can use circuit animation, whereby the computed data are displayed and updated on your schematic.

button in the Main Toolbar. But getting meaningful results requires a few more steps. A simulation needs an input such as a source as well as a probe or some kind of virtual instrument to measure the result. Inputs can be source devices found in the supplied parts database. These include voltage sources or current sources that supply power to your circuit. Alternatively, you can use the Power Supply or Function Generator in the Virtual Instruments panel to set up stimuli. To measure the results, you can use the Virtual Oscilloscope, Voltmeter, Ammeter or one of the other meters found in the Virtual Instruments or you can use circuit animation, whereby the computed data are displayed and updated on your schematic.

Set up the appropriate stimulus and meter, set the time step you desire and click the green RUN ![]() button to start the simulation. Click the Pause

button to start the simulation. Click the Pause ![]() button in the toolbar to pause the simulation. Click the green arrow

button in the toolbar to pause the simulation. Click the green arrow ![]() again to resume the simulation or click the Strop/Reset

again to resume the simulation or click the Strop/Reset ![]() button to reset the time to t = 0. The current time is displayed in the simulation toolbar next to the control buttons. The simulation mode is controlled by the main toolbar and consists of the Reset, Pause, Step, Walk, and Run buttons. These buttons control the progress of operation of the live simulation. The Step Ceiling and Update Interval settings control how the simulation progresses and how often the results are updated. The Step button increments the simulation time by one time step and pauses. Each subsequent click of the Step button increments the simulation by another time step. The Walk button starts the simulation but increases the simulation time by the walk factor, which can be set in the Simulation | Time Options menu.

button to reset the time to t = 0. The current time is displayed in the simulation toolbar next to the control buttons. The simulation mode is controlled by the main toolbar and consists of the Reset, Pause, Step, Walk, and Run buttons. These buttons control the progress of operation of the live simulation. The Step Ceiling and Update Interval settings control how the simulation progresses and how often the results are updated. The Step button increments the simulation time by one time step and pauses. Each subsequent click of the Step button increments the simulation by another time step. The Walk button starts the simulation but increases the simulation time by the walk factor, which can be set in the Simulation | Time Options menu.

A live simulation runs a perpetual transient simulation of your circuit starting at time t = 0 and increments the time by the Step Ceiling setting. Results of the simulation are displayed in either the animated schematics or any of the virtual instruments. The results are refreshed by the time specified in the Update Interval setting.

B2.Spice A/D allows both analog and digital stimuli for live simulations. For analog stimuli, you can use the voltage and current sources or the Function Generator or Power Supply in the Virtual Instruments panel. For a digital stimulus, you can use a digital input or a digital source. Note that when you place a voltage or current source in a circuit, Workshop automatically adds a corresponding Function Generator for you. The voltage and current source's transient properties can be set in the transient page of their property dialogs. This allows a variety waveforms including sinusoidal, triangular, square, exponential, piecewise linear, etc.

The voltmeter, ammeter, and markers all can be used to probe voltages and currents for all simulations. In order to use the marker as a voltage probe, check the checkbox by that name in its property dialog. You can also probe the circuit using the Virtual Instruments such as the oscilloscope, voltmeter, ammeter, wattmeter, etc. Note that virtual voltmeters and ammeters are added to the virtual instrument panel automatically every time you place a voltmeter or ammeter in your schematic. The voltage across the voltmeter, the current through each ammeter, and the voltage at each marker will show up in the various Virtual Instruments depending on their transient or frequency requirements. For more information, refer to the virtual instruments section. You can also display the results of a live simulation using Circuit Animation. In that case, the voltage, current or power data appear on the schematic next to the nodes, wires or devices either as text or graphically as colored wires.

Additional Considerations for a Successful Simulation

B2.Spice A/D operates based on a large number of numerical simulation parameters with default values. In most cases, you do note have to worry about setting or changing these values. However, in certain cases, the simulation of your circuit may not converge or hit a singularity. Then you might be able to improve the simulation speed by adjusting certain parameters. You do this through the simulation options. The options are accessed through the Simulation | Set Simulation Options menu. The options are divided up into three tabs in the dialog: Convergence, Mixed-Mode, and Miscellaneous. For details on these parameter, see the section on Simulation Options.

Running RF.Spice A/D Tests

From the Toolbox's Tests tab, you can select, set up, and control any number of tests that can be performed on your circuit. To select a Test and to set it up, click on the "Tests" tab in the Toolbox. The Test Panel shows a list of the available tests with respective checkboxes. Click the "Setup" button next to each test type to set its properties and various available options and settings. Click the green "Run Enabled Tests" button to start the test(s). To learn more about individual tests, please see the section on Tests.

At the bottom of the test panel are three tabs that allow you to run different variations of the selected test. The first tab, Single Test, is a single run through the selected test type using the specified test setup parameters. A graph, table or both can be specified to display the test results. The "Preset Plots" button will allow the specification of plots to display before the test is run. Otherwise, Workshop will automatically plot any meter signals as well as signals specified by the use of Markers.

The Sweep tab allows sweeping of multiple parameters over the test range. For instance, a resistor’s resistance can be stepped from 1K to 10K, with increments by 1K, over the range of a Transient Test. This will actually run 10 Test runs, with the first run having the resistor’s value at 1K, the second will run with the resistor’s value at 2K, and so on, until the resistor’s value is 10K. You can do multilevel sweeps by specifying more than one parameter to sweep, but care must be used, as this will exponentially increase the number of test runs. The Sweep setup button brings up a box that allows you to specify which parameters and how they are swept. The table format is similar to the Live Circuit panel. Select a parameter to sweep and click the Setup Sweep Parameter to set up the sweep parameters. The Monte Carlo Test is similar to the Sweep tests, but the parameter values are varied at random, limited to a user-specified range. The Monte Carlo Setup specifies which parameter to vary and how to randomly vary it.

RF.Spice A/D Test Types

The following is a list of B2.Spice's available test types. Click on each link to read more details about each individual test type.

Simulation Options

The simulation options have various purposes. The options are accessed through the "Simulate > SPICE Simulation Options" menu. The options are divided up into three tabs in the dialog: Convergence, Mixed-Mode, and Miscellaneous.

Temperature options

Temperature options can be found under the Miscellaneous Options tab. To set the operating temperature for the simulation, use temp. Tnom is used to set the temperature at which the model parameters were measured at. Don’t use this unless you create custom models and you know what temperature you measured their parameters at.

Convergence options

There are a lot of options available to help with simulation convergence. This reflects the difficulty in getting some circuit simulations to converge.

For operating point convergence, some particularly useful options are itl1, rshunt, reltol, gmin, gminsteps, vntol and abstol. Itl1 is the iteration limit for the operating point and increasing it from 40 to a higher value will help with convergence. Rshunt is the resistance from every node to ground. It defaults to a very high value (1e12). Lower values may help convergence, but lower values also could alter circuit behavior. Reltol, the relative error tolerance, can be increased to help convergence, but at the price of accuracy. If it's too high, then you may get incorrect results as is the case with a simple feedback op-amp circuit with the opamp from the devices menu. Gmin is the minimum conductance. It's used internally across junctions in transistors and diodes. If it's too small, the simulator can fail to converge. If you set it to high, however, it can affect the simulation results. Set it as high as possible without it affecting the simulation results.

Gminsteps is used in the gmin stepping part of the operating point solution. It tries to solve the circuit with various values of gmin. The higher the value of gminsteps, the better the chance for convergence.

Vntol and abstol go along with reltol in determining the error tolerance. They are useful when the node voltage or branch current approach zero and the relative tolerance becomes too constraining.

Itl6 is also helpful for operating point convergence.

Normally, itl6 should be left at zero. However, if the operating point won't converge even after using the options described above and other techniques given in the section on Operating Point Success, then Itl6 can be used. Itl6 activates the source stepping algorithm and sets the maximum number of total iterations for the source stepping algorithm. It is the same as srcsteps.

For dc sweep convergence, itl2 is useful. Increase it to help the simulator converge.

For transient convergence, a number of other options are relevant. itl4 controls the number of iterations in the transient solver at a given timepoint. Increase it to a larger value, e.g. 200, to help with convergence but this may not be enough.

Trtol and chgtol are not tolerance parameters. Trtol is related to truncation error in the Local Truncation Error timestep control algorithm that is used with the transient simulation. It is related to the timestep during the transient simulation. Chgtol is also used in the LTE algorithm. It's purpose is to prevent the transient from locking up. Both of these should not be used unless you are a spice expert.

Minbreak is the minimum break between timepoints while running a transient simulation. For very sharp transitions, minbreak should be reduced. Breakpoints are inserted by the piecewise linear sources and pulse sources and indicate changes in inputs to the circuit.

Pivtol and Pivrel are used in the numerical pivoting algorithm. Pivtol is the minimum acceptable value for a pivot and pivrel is the minimum ratio between a pivot entry and the largest entry in a column of the conductance matrix. Only expert spice users should use these.

Method switches between integration algorithms for calculating capacitor voltages and inductor currents for transient solutions. The possible values are gear for the gear method and trap for the trapezoidal method. The default is trap. Maxord goes along with the gear method and is the maximum order for the multiorder integration method. Higher values of maxord are more accurate but may slow down the simulation.

Mixed-Mode Circuit Options

Some options relate to the analog to digital and digital to analog converters that B2.Spice automatically inserts between analog and digital portions of the circuit. The parameters bb_daOutlow, bb_daOutHigh, bb_adInLow, and bb_adInHigh are for low and high output voltages for D/A converters and for low and high threshold voltages at the input of A/D converters. Bb_daOutX is the indeterminate voltage at the output of the d-to-a converter.

Maxopalter is used in operating point analysis for the maximum alternations between analog and event solutions. Maxevtiter is the maximum number of iterations for event solution. Noopalter prevents the simulator from alternating between analog and event solutions. Ramptime is the transient analysis supply ramping time, but it only seems to be used with xspice models for the capacitor and inductor (rather than the regular spice capacitor and inductor.)

ConvLimit enables convergence assistance for xspice models. ConvStep controls the size of the step between iterations on xspice model inputs. ConvAbsStep controls the maximum absolute step between iterations on xspice model inputs.

Miscellaneous Options

Defl and defw are the default mosfet length and width. You can override these in specific mosfets. They default to 100 microns if left blank. Defad and defas are the default drain and source mosfet areas.

Oldlimit uses old Spice2 mosfet limiting, and badmos3 uses the old mos model. I don't know why you would want to use either of these.

Bypass allows the device calculations to bypass updating values for unchanging elements. I presume that this would speed up the simulation.

Trytocompact is used with transmission lines.

Keepopinfo is not used by B2.Spice A/D.

For more information on these options, see Inside Spice by Ron Kielkowski published by McGraw Hill.

Summary

| Option Name | Option Description |

|---|---|

| gmin | Minimum conductance |

| reltol | Relative error tolerance |

| itl1 | DC iteration limit |

| itl2 | DC transfer curve iteration limit |

| itl4 | Upper transient iteration limit |

| itl6 | Number of source steps |

| gminsteps | Number of Gmin steps |

| shunt | Shunt resistance from analog nodes to ground (XSPICE) |

| abstol | Absolute error tolerance |

| vntol | Voltage error tolerance |

| Method | Integration method |

| Maxord | Maximum integration order |

| bb_daOutLow | Low output voltage for implicit D to A converters (XSPICE) |

| bb_daOutX | Indeterminate output voltage for implicit D to A converters (XSPICE) |

| bb_daOutHigh | High output voltage for implicit D to A converters (XSPICE) |

| bb_adInLow | Low Input voltage threshold for implicit A to D converters (XSPICE) |

| bb_adInHigh | High Input voltage threshold for implicit A to D converters (XSPICE) |

| bb_daTLH | Low-To-High delay for implicit D to A converters (Xspice) |

| bb_daTHL | High-To-Low delay for implicit D to A converters (Xspice) |

| bb_adTLH | Low-To-High delay for implicit A to D converters (Xspice) |

| bb_adTHL | High-To-Low delay for implicit A to D converters (Xspice) |

| maxopalter | Maximum analog/even alternations in DCOP (XSPICE) |

| maxevtiter | Maximum event iterations at analysis point (XSPICE) |

| noopalter | Do not do analog/even alternation in DCOP (XSPICE) |

| ramptime | Transient analysis supply ramping time (XSPICE) |

| convlimit | Enable convergence assistance on code model (XSPICE) |

| convstep | Fractional step allowed by code model inputs between iterations (XSPICE) |

| convabsstep | Absolute step allowed by code model inputs between iterations (XSPICE) |

| autopartial | Use auto-partial computation for all models (XSPICE) |

| Noopiter | Go directly to gmin stepping |

| trtol | Truncation error overestimation factor |

| chgtol | Charge error tolerance |

| pivtol | Minimum acceptable pivot |

| pivrel | Minimum acceptable ratio of pivot |

| tnom | Nominal temperature |

| temp | Operating temperature |

| oldlimit | Use SPICE 2 MOSFET limiting |

| defl | Default MOSFET length |

| defw | Default MOSFET width |

| minbreak | Minimum time between breakpoints |

| defad | Default MOSFET area of drain |

| defas | Default MOSFET area of source |

| bypass | Allow bypass of unchanging elements |

| trytocompact | Try compaction for LTRA lines |

| badmos3 | use old mos3 model (discontinuous with respect to kappa) |

| Method | Integration method |

| Maxord | Maximum integration order |

| srcsteps | Number of source steps |

| keepopinfo | Record operating point for each small-signal |

Setting Initial Conditions

Setting the initial guess for DC operating point

To set the initial guess at a node, place a Marker component (it's available in the devices menu) in the circuit and attach it to the node. Then double-click on the Marker, which will open a dialog box. Set the initial guess to the appropriate value, and then select OK to close the dialog box. Then select Simulation Setup from the Simulation menu, and activate the checkbox next to Initial Guess (NodeSet).

Setting Transient Initial Conditions

To set the transient initial conditions at a node, place a Marker component (it's available in the devices menu) in the circuit and attach it to the node. Then double-click on the Marker, which will open a dialog box. Set the initial condition to the appropriate value, and then select OK to close the dialog box. Then select Simulation Setup from the Simulation menu, and activate the checkbox next to Initial Conditions.

Tips for Simulation Success

All simulations run an operating point analysis at least once during the simulation. If the operating point analysis fails, then the simulation will fail. If you are having problems with any one simulation, then the best approach for identifying the problem is to run an operating analysis by itself.

Operating Point Success

When you run a simulation, the simulation engine attempts to find a stable operating point for the circuit. In some cases, it fails. Possible reasons include circuit topology, bistable or unstable circuits, far-off initial node guesses. In addition, highly non-linear circuits are difficult for the simulator to handle and may require tweaking options. Error messages include "Iteration limit reached" and "singular matrix" or "gmin stepping failed". Look in log window after simulation is complete to find error messages.

Common problems/solutions include:

Check your node connections. Use Show Node Numbers from the View menu to check node numbers. Nodes with the same number are connected. Also, you can check the spice netlist for node numbers of devices. Often problems result from missed connections or unintentional connections.

Check for illegal configurations: Voltage sources in parallel, inductors in parallel, voltage source in parallel with inductor. In this case, add small resistor in series with vs or inductor.

current sources in series, capacitors in series, current source in series with capacitor. In this case, add large resistor in parallel with the capacitor or current source.

Check for typos: A common error is confusing zero with the letter "O" for parameter values.

If you can't find a simple error in the circuit, then try one or more of following:

increase itl1 (e.g. 200)

Use shunt resistances: Reduce RSHUNT (e.g. 1e9) low enough to have an impact on the convergence but not so low that it affects the behavior of the circuit.

increase error tolerance: This is the option reltol.

increase minimum conductance: Option Gmin.

NODESET: Set the initial guess at different troublesome nodes in the circuit. Do this by checking the box in simulation set-up for Nodeset, and by adding markers in the circuit at nodes, and setting the initial guess of the markers.

Active Devices Off: When Spice starts a simulation, it assumes, by default, that all active devices are in their active regions. Sometimes setting some active devices to OFF will help in circuits with hysteresis or with multiple feedback paths.

Transient Success

Common error message: Timestep too small. This occurs when the simulator gives up after reducing the timestep below the minimum time step.

There are several options you can try to improve the results.

Simulation Option: Increase itl4 (transient iterations) , e.g. 200. This allows more tries before giving up.

Simulation Option : ITL5: This sets the maximum number of total iterations. It defaults to 5000. Try increasing it.

Make your circuit more realistic. Most importantly, add junction capacitances on transistors. These are in model parameters for transistors.

Decrease shunt resistance: Decrease the value of the shunt resistance using Set Simulation Options.

Simulation Option : RELTOL: This is the relative error tolerance. The default is 0.1%. Try increasing it by a factor of 10, to 1.0 %. This is very useful in solving convergence problems due to the small time step of the transient algorithm.

Increase the absolute current tolerance

Special Notes for the Op Amp

The op-amp model used for the 5-pin opamp is highly non-linear and it will give the wrong results in some cases with default tolerances. To fix this, decrease the relative tolerance option to a very low value (e.g. 1e-7). In general, if the results are looking fishy, decrease the relative error tolerance.

Additional Material

The first three buttons control how often the graph view is updated while simulation results are received by the workshop. Obviously, updating the graph more often will slow down the operation of the program.

The option to replace old simulation results prevents the workshop from getting overly cluttered from many graphs and text simulation results.

Checking the "Run simulation with interactive communications" box will allow you to view the simulation results while they are being generated, and this will also allow you to pause and stop the simulation in progress. Leaving it unchecked will run the simulations in batch mode, which cannot be stopped or paused, and will not display a graph until the simulation is complete. Batch simulations are generally faster.

Generate extra signals will generate signals for device currents in the circuit (e.g., inductor currents) and also internal device node voltages, e.g. if a diode has a resistance, then the voltage between the actual diode and its internal resistor.

Generate deep results generates signals inside of subcircuits. At a minimum, subcircuit node voltages and branch currents will be enabled. If Generate Extra Signals is enabled, then the extra signals inside of subcircuits will be generated also.

Generate all Top-level Currents will generate all possible current signals for each node.

The Spice program specification allows you to modify the spice simulation engine file path.

The simulation data directory specifies in which directory temporary data files are written to.